Parmi les résultats obtenus par l’European Processor Initiative, la preuve de concept réalisée sur l’accélérateur EPAC, ci-dessus. (Crédit : EPI)

L'European Processor Initiative, qui réunit 28 acteurs technologiques de l'UE pour concevoir un processeur HPC européen, a présenté ses 1ers résultats. Outre les spécifications architecturales du Rhea, 1čre génération du processeur universel de l'EPI, le projet a réalisé une preuve de concept d'un accélérateur et un microcontrôleur haute performance embarqué pour les applications de la filičre automobile.

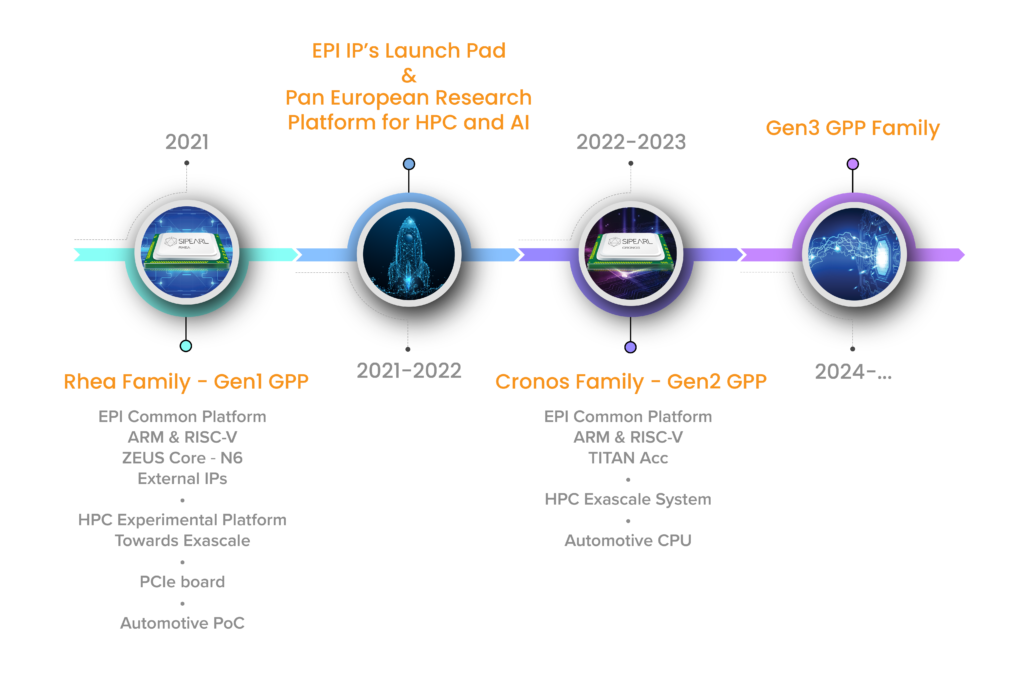

Le monde du calcul haute performance développe un processeur européen pour permettre ŕ l'UE d'acquérir une indépendance sur les technologies de puces et d'infrastructures pour les supercalculateurs exascales. Lancé en 2018, l'European Processor Initiative (EPI) rassemble un consortium de 28 partenaires de 10 pays (*). Le projet vient d'achever une premičre phase de trois ans et les résultats obtenus ont été communiqués la semaine derničre dans les trois principaux champs de recherche explorés : un processeur universel (GPP, general purpose processor), des accélérateurs et des applications dans la filičre automobile.

C'est le constructeur français Atos/Bull qui pilote le premier champ de recherche avec la société franco-allemande SiPearl. Ensemble, ils ont défini les spécifications architecturales du microprocesseur haute performance et basse consommation Rhea destiné au supercalculateur exascale européen. « Avec 29 coeurs Risc-V, l'achitecture Arm Neoverse V1 utilisée par SiPearl pour concevoir le Rhea offrira une solution efficace, évolutive et personnalisable pour les applications HPC », indique l'EPI dans son communiqué. Le consortium estime que les résultats obtenus dans cette premičre phase du projet vont ętre déterminants pour le lancement de supercalculateurs exascales européens en 2023.

La premičre génération de puce HPC développée par l'European Processor Initiative combine des coeurs Risc-V , et l'achitecture Arm Neoverse V1. (Crédit EPI)

Un prototype virtuel du processeur

SiPearl a optimisé un NoC (réseau-sur-puce) pour les transferts de données ŕ haute fréquence et large bande passante entre les coeurs, les accélérateurs, les entrées/sorties et les ressources de mémoire partagée. Le communiqué de l'EPI ajoute qu'un prototype virtuel du processeur a été conçu et utilisé pour effectuer des estimations de performance et de tout premiers développements logiciels. Le processeur Rhea va intégrer les technologies des partenaires du projet EPI sur l'architecture mémoire, l'optimisation de la bande passante, la sécurité et la gestion de la consommation électrique. Concernant la mémoire, pour aider ŕ évaluer les choix architecturaux, le CEA a développé une plateforme de simulation pour analyser l'efficacité du contrôleur dans le pilotage des mémoires HBM2E ŕ large bande passante.

Sur les fonctionnalités embarquées de sécurité, ProvenRun apporte sa technologie stand-alone de gestion de la sécurité pour processeur HPC et edge, et l'Université de Pise sa technologie Crypto Tile. Cette derničre comprend un module matériel pour le chiffrement symétrique (AES avec 9 modes de chiffrement), asymétrique (ECC, ECDSA, ECIES, ECDH) et de hachage (SHA2/SHA3). L'EPI précise que ce module offre plusieurs ordres de grandeur dans l'augmentation de la bande passante et la réduction de la consommation par rapport ŕ une solution logicielle. Crypto Tile inclut aussi la configuration et le stockage sécurisé des clés, une protection contre les attaques par canaux auxiliaires (side-channel) et la génération de nombres aléatoires sur puce (TRNG), notamment. Le support du chiffrement post-quantique est fourni par la mise en oeuvre d'algorithmes tels que Kyber et Dilithium. Dans le domaine de la consommation d'énergie, un contrôleur open source basé sur une architecture Risc-V a été conçu par l'Université de Bologne et l'ETH Zürich et intégré au processeur Rhea. Il exploite des algorithme d'IA pour la gestion de l'énergie sur SoC ŕ grande échelle. Par ailleurs, Atos et E4 Computer Engineering ont mis au point une plateforme de référence de test de gestion de l'énergie en s'appuyant sur des composants de STMicroelectronics. A l'issue de cette premičre phase de 3 ans, le projet de processeur de l'EPI a atteint un statut d'achčvement de niveau RTL (register transfer level, description des architectures microélectroniques), indique le consortium. La conception est en au stade de la validation ŕ travers des émulations.

Une accélération économe en énergie pour le HPC et l'IA

Le consortium européen travaille aussi sur un accélérateur de calcul, EPAC (European processor accelerators), économe en énergie pour les charges de travail HPC et IA. Il estime qu'avec la preuve de faisabilité réalisée sur l'EPAC, il a pu démontrer qu'il était possible de créer une conception exclusivement européenne, en s'appuyant sur une architecture de jeu d'instructions open source. L'EPAC combine plusieurs technologies d'accélération spécialisées pour différentes applications. Ces travaux font intervenir SemiDynamics, le Barcelona ComputingCenter et l'Université de Zagreb, ainsi que Chalmers, Forth, Fraunhofer, ETH Zürich et le CEA.

Enfin, le troisičme champ de développement de l'initiative européenne concerne la filičre automobile. Dans ce domaine, le projet EPI a mis au point une preuve de concept pour une plateforme de calcul haute performance embarquée (eHPC) et un SDK associé. Ces développements sont coordonnés par Infineon. Une principale réalisation a été démontrée dans une BMW X5, sur un PoC d'une unité de microcontrôleur eHPC intégrée dans une plateforme modulaire intégrant plusieurs technologies du consortium EPI. Différents essais ont été réalisés pour collecter des données et évaluer des scénarios de test impliquant des paramčtres de conduite autonome.

Eric Monchalin (Atos), président du conseil d'administration de l'EPI, souligne les résultats exceptionnels obtenus par les équipes du projet européen aprčs ces trois années de coopération. Les objectifs ont été atteints dans les temps avec un budget limité, malgré les conditions de travail imposées par la pandémie. « Cela a créé des conditions favorables au lancement de la phase suivante et pour la livraison des processeurs et accélérateurs européens pour les projets EUPEX (european pilot for exascale) et TEP (european pilot), les précurseurs des systčmes exascales européens », écrit-il.

(*) Les membres du consortium EPI : Atos, BSC (Barcelona supercomputing center), Infineon, Semidynamics, CEA, Chalmers, ETHZürich, Forth, Genci, Técnico Lisboa, le centre de recherche de Juliers (Jülich Forschungszentrum), Alma Mater Studiorum (Université de Bologne), Faculty of electrical engineering and computing (Université de Zagreb), Fraunhofer, ST Microelectronics, E4 Computer engineering, Université de Pise, Surf Sara, Kalray, Extoll, Cineca, BMW Group, Elektrobit, ProveRun, Karlsruher Institut für Technologie, Menta, SiPearl et Kernkonzept.

Suivez-nous